WCCFtechは2日(現地時間)、米インテルの次々世代マイクロアーキテクチャ「Cannonlake」においても、一般ユーザー向けのSKUでは最大8コア構成が継続される見込みと伝えています。

WCCFtechによると、世界的に利用されているビジネス特化型SNS、LinkedIn上において、Cannonlakeの開発に携わるインテルのエンジニアが同アーキテクチャに関する情報を明らかにしたとのことです。

エンジニアのプロフィール内には、同氏が「CFF(Converged Coherent Fabric)」と呼ばれる新たな高速インターコネクト技術の開発に携わっていることに加え、Cannonlake世代のCPU製品においては4コアないし6コア、あるいは8コア構造が採用される予定であることが明記されています。

これまで8コアのCPUを搭載する製品は、ハイエンドデスクトップ向けあるいはサーバー向けのハイエンド帯のSKUに限られてきており、メインストリーム帯のSKUにおいては最大でも4コア構成までとされてきました。一方で、HPCや高性能サーバーなどの特殊な用途向けのSKUには、既に8コア以上のCPUを搭載する製品も存在しています。

LinkedIn上に公開されていたプロフィール

現時点では、プロフィール内の記述がメインストリーム帯のSKUについて言及したものなのか、はたまたハイエンド帯に関する情報なのかは定かではありませんが、もしかするとついにインテルはCannonlake世代においてメインストリーム帯における「4コア制限」の解除を決定したのかもしれません。

とは言うものの、やはりメインストリーム帯においては4コア製品までとされ、8コア製品が提供されるのは従来通りハイエンド帯のみに限られることになるという予測の方が、少なくとも現時点ではより現実味が感じられるのではないでしょうか。

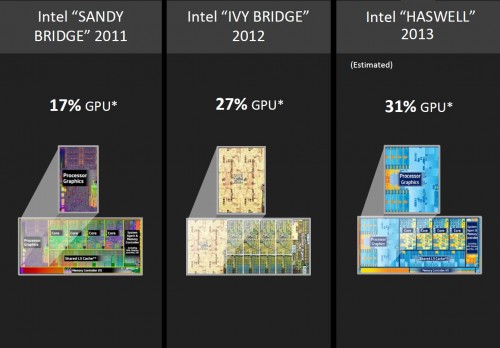

年々増加するダイ面積におけるGPUコアの占有率

なお近年のインテルは、特にメインストリーム帯のCPU製品においてGPUコアの強化を推進しており、数年前の製品と比較してダイ面積におけるGPUコアの割合は着実に増加傾向にありますが、仮に従来の2倍にも相当する数のCPUコアを搭載すれば、当然ダイ面積におけるCPUコアの占有面積は増加することになりますので、その分GPUコアが圧迫されることが予想されます。

一方で、Cannonlakeの製造においてはより微細化された「10nm FinFET」プロセスが採用されることとなりますので、懸念されるダイ面積に関する課題は、プロセス微細化の恩恵でクリアできるのかもしれません。

残念ながら現時点で確定的な情報はほとんど存在していませんが、少なくともCannonlakeが2017年内に登場する予定であることだけは間違いなく、また来年には米AMDの次世代マイクロアーキテクチャ「Zen」も登場することを踏まえると、来年以降のCPU業界はここ数年間と比較して遥かに面白い展開を見せることとなりそうです。

[WCCFtech]